| 學程簡介 | 課程大綱 | 課程預覽 | 會員優惠 |

➤ 獨家資深業師授課!提供課程答疑平台,訓中訓後為學員排難解惑。

📌 本課程可申請補助:大人提、小人提、退輔會補助適用

AI 深度學習、5G 通訊、無人駕駛、邊緣運算與高速影像處理,正在重新推動硬體運算架構的重要性。當系統需要更高效能、更低延遲、更低功耗與更高安全性時,單靠 CPU 或一般軟體架構,已經無法滿足所有應用需求。FPGA 晶片,正是實現高效能、低延遲與客製化硬體運算的重要解決方案。但在 AI 快速發展的今天,學 FPGA 的意義已經不只是「學會寫 Verilog」。因為 AI 工具已經可以輔助產生程式碼,甚至可以嘗試產生 RTL Code。

真正關鍵的是:

你是否看得懂 RTL 背後的硬體行為?

你是否能判斷這段設計是否可綜合、可驗證、可除錯?

你是否知道它在真實 FPGA 晶片上能不能穩定運作?

FPGA晶片,正是實現這些目標的重要解決方案!

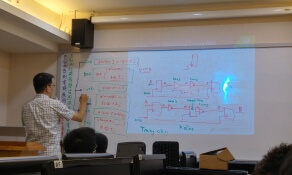

艾鍗學院特別邀請具 16 年以上 FPGA / 數位 IC 設計經驗的一線資深工程師,規劃「FPGA 數位 IC 設計實戰」課程。本課程不是把 Verilog 當成另一種程式語言來教,而是從數位電路設計思維出發,帶你理解 RTL 如何對應到真實硬體電路。課程分為三個階段:

第一階段從數位電路基本概念、組合邏輯、序向邏輯、FSM 有限狀態機與 Verilog HDL 開始,建立 RTL 設計的核心觀念。

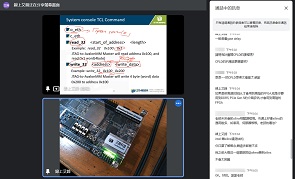

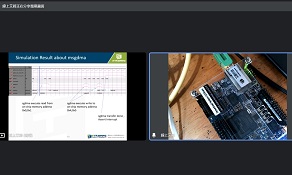

第二階段進入 FPGA 晶片設計實務,透過 UART、SPI、I2C 等常見介面電路,搭配 Testbench、Simulation、ModelSim、SignalTap 與 Timing Constraint,培養從設計、驗證到除錯的實戰能力。

第三階段延伸至 SoC FPGA 系統整合,學習 Platform Designer、Avalon Bus、IP Component 與 NIOS-V MCU,建立軟硬整合與系統化設計能力。

透過本課程,你學到的不只是 Verilog 語法,而是 AI 時代更稀缺的能力:理解電路、設計架構、驗證邏輯、判斷 RTL 是否可靠,並把設計真正落地到 FPGA 硬體上。

這門課帶你建立四個核心能力

講師結合業界一線 FPGA / 數位 IC 設計經驗與艾鍗長期工程師培訓經驗,帶你從觀念、設計、驗證到系統整合,建立真正能落地的 FPGA 實戰能力。

✔ 看得懂 RTL 背後的電路行為

不是只背 Verilog 語法,而是理解每一段 RTL Code 對應到什麼硬體邏輯,例如暫存器、計數器、狀態機、組合邏輯與序向邏輯。

✔ 寫得出可綜合、可維護的硬體描述

學會用正確的硬體設計思維撰寫 Verilog,避免用 C、Python 等軟體流程思維來寫 RTL,降低產生不可綜合、難除錯或時序不穩定設計的風險。

✔ 驗得出設計是否正確

透過 Testbench、Simulation、ModelSim、SignalTap、SignalProbe 與 Timing Analyzer,建立燒錄前模擬驗證與燒錄後實機除錯能力。

✔ 整合得出完整 SoC FPGA 系統

從 UART、SPI、I2C 介面實作,到 Platform Designer、Avalon Bus、IP Component 與 NIOS-V MCU,建立 FPGA 與嵌入式系統整合能力。

Why SoC FPGA? 為什麼要學軟硬整合?

現代嵌入式系統不再只是單純寫韌體,也不只是單純做硬體。許多產品同時需要軟體的彈性、硬體的高速並行運算、低延遲反應、高效能資料處理,以及可客製化的系統架構。SoC FPGA 正是結合這些需求的解決方案。

SoC FPGA 將處理器系統與 FPGA 可程式邏輯整合在同一個平台上。開發者可以使用 CPU 處理控制流程、作業系統與周邊管理,也可以使用 FPGA 實作高速資料處理、訊號處理、通訊介面或客製化硬體加速。在 AIoT、邊緣運算、工業控制、影像處理、通訊系統與客製化硬體加速場景中,SoC FPGA 能讓產品同時具備效能、彈性與開發速度。本課程透過 Platform Designer、Avalon Bus、IP Component 與 NIOS-V MCU,帶你理解 SoC FPGA 如何從硬體設計走向完整系統整合。

FPGA, SoC FPGA, Verilog HDL, RTL Design, 數位 IC 設計, FSM, Testbench, Simulation, ModelSim, SignalTap, Timing Constraint, TimeQuest, Intel Quartus Prime, Altera MAX 10, Avalon Bus, IP Core, Platform Designer, NIOS-V, FPGA Validation, 硬體設計, 軟硬整合

Jemmy (講師具16年數位IC設計經驗)

▪ 電機工程碩士 ▪ 資深數位IC設計工程師

▪ FPGA/CPLD設計 ▪ Verilog HDL ▪ Gigabit Ethernet網路介面訊號處理

▪ FPGA SoC系統設計 ▪ 數位電路分析設計 ▪ 數位晶片產品開發

─ 演算法與架構並存的時代,用FPGA以更快的速度把產品做出來

Ted Chang (講師具16年數位IC設計經驗)

▪ EE工程碩士 ▪ 資深數位IC設計工程師

▪ FPGA/ASIC設計 ▪ RTL Design, FPGA Validation ▪ 系統晶片設計與整合

▪ Gigabit Ethernett, TDM over IP, video over data design

▪ ARM SOC AXI/AHB/APB ▪ IC電路模擬測試 ▪ Verilog /VHDL

─ 雖然資深但是不間斷Learning

-

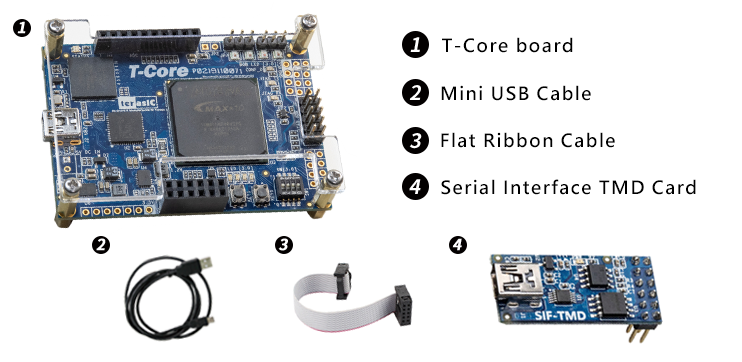

Altera MAX 10 FPGA:T-Core

▪ Programmable FPGA元件

- MAX 10 10M50DAF484C7G 元件

- 集成雙ADC,每個ADC支持1個專用模擬輸入引腳和8個雙功能引腳

- 50K 邏輯單元

- 1638Kb M9K 塊

- 144 个 18x18 乘法器

- 4 個鎖相環

▪ 通用介面

- 4 個綠光 LED

- 4 個紅光 LED

- 4 個滑動開關

- 2 個去抖動按鈕

▪ JTAG

- 板載USB Blaster II下載電路用於下載MAX10

- 板載USB Blaster II下載電路用於下載RISC-V 程式

- JTAG Master功能用於下載別的板子上的FPGA

▪ Clock與記憶體元件

- 兩個50 MHz Single-ended,外部 Oscillator Clock源

- 一個10 MHz Single-ended,外部l Oscillator Clock源

- 64Mb QSPI Flash (用於儲存 RISC-V 程式)

▪ 擴充介面

- 2x6 TMD 擴充接頭

- 1x10 ADC 接頭

- 兩個 1x3 RGB LED 擴充接頭

▪ 電源供應

- USB Type mini-AB Port (5V)

- 2-pin 擴充電源接頭 (4.4-5.6V)

▪ 連接性

- 連接 BTS-TMD

- USB-Blaster II 下載線

- 連接 WS2812B LED Strip

完成本課程後,你將具備以下能力:

1、建立數位電路設計的基本概念,理解組合邏輯、序向邏輯與狀態機設計方式。

2、理解 Verilog HDL 與真實硬體邏輯電路之間的對應關係。

3、能夠閱讀 RTL Code,判斷其背後描述的是什麼硬體行為。

4、學會 FSM 有限狀態機設計方法,能將功能需求轉換成狀態規劃與狀態轉換。

5、熟悉 Testbench 撰寫與 Simulation 流程,在燒錄前驗證 RTL 設計是否正確。

6、實作 UART、SPI、I2C 等常用週邊介面,強化 FPGA 實務設計能力。

7、學會 FPGA 專案建立、編譯、燒錄與基本除錯流程。

8、學會使用 SignalTap、SignalProbe、ModelSim 等工具分析與驗證硬體行為。

9、理解 Timing Constraint 與 TimeQuest Timing Analyzer,確保設計在時序上正確運作。

10、掌握 Platform Designer 的使用,能整合多個 IP 模組進行系統化設計。

11、透過 NIOS-V MCU 實作,理解 SoC FPGA 的軟硬整合流程。

12、培養 AI 時代最重要的 RTL 判斷力:不只會產生 Code,更能判斷 Code 是否可用、可靠、可落地。

2、已具備 MCU 或嵌入式系統經驗,想往硬體加速與 FPGA 發展者

3、想轉職或補強數位 IC / FPGA 工程能力者

4、想在 AI 時代保有硬體工程判斷力者

5、電子、電機、資訊、通訊、自動控制與半導體相關背景者佳.

學完本課程後,可銜接 FPGA 設計、RTL Design、數位 IC 設計、FPGA Validation、SoC FPGA 系統整合與嵌入式硬體加速等職涯方向。

※104人力銀行調查: 數位IC設計工程師類薪資